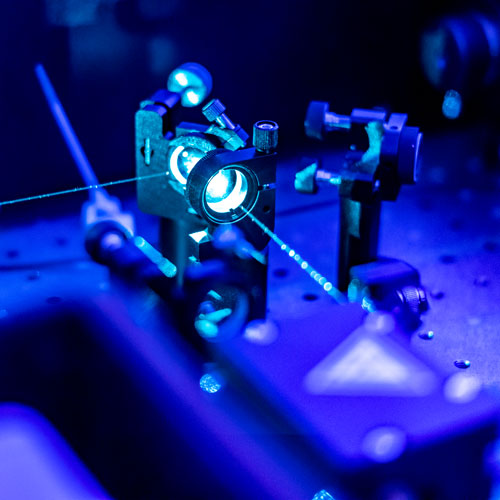

Posouváme hranice

Provádíme výzkum a vývoj v oblasti informačních a komunikačních technologií. Výsledky výzkumu uvádíme do praxe rozšiřováním portfolia našich služeb a jejich vylepšováním.

Podporujeme rozvoj, osvojování a efektivní využívání nejmodernějších komunikačních a informačních technologií.